基于FPGA的GPS时钟驯服电路设计与实现.pdf

时间:08-22 11:36

查看:1955次

下载:162次

简介:

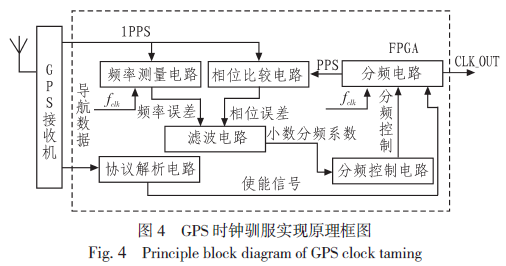

为满足系统对高精度时钟的要求,根据晶振时钟无随机误差和全球定位系统(GPS)时钟无累计误差的特点,提出了一种利用GPS 秒时钟驯服晶振时钟来实现高精度时钟的方案。该方案根据数字锁相环倍频原理,通过测量GPS 秒时钟和本地生成秒时钟的相位误差来调整电路分频比,实时消除晶振时钟的累计误差,从而实现高精度的系统时钟。经实际验证,该方法在使用16.369 M 温补晶振时,在GPS 信号有效情况下输出时钟误差小于0.1 ppm,GPS 信号失效后1 小时后误差小于0.3 ppm。